Government

News and insights to help government IT professionals improve public services as well as help businesses understand how law and policy impacts their IT strategy. Coverage includes government support for IT innovations, examinations of regulations and policymaking that businesses may have to adhere to, motivations behind public and private positions on technology, and the approach government agencies take regarding data, commerce, consumer protections, and privacy.

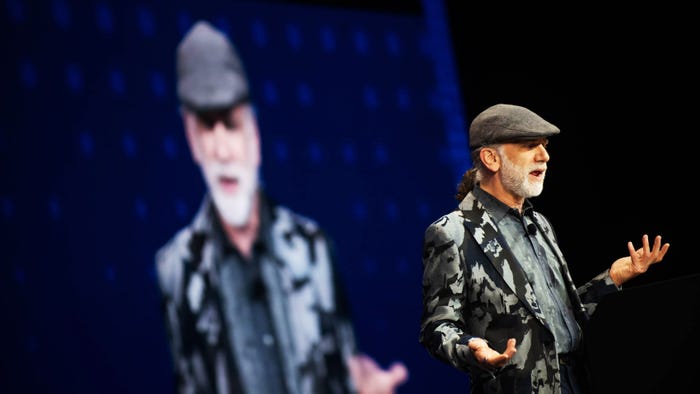

Paul Nakasone, former director of the National Security Agency, and a former commander of US Cyber Command, speaks at the RSA Conference 2024.

Cyber Resilience

Four Horsemen of Cyber Reunite at the RSA ConferenceFour Horsemen of Cyber Reunite at the RSA Conference

Paul Nakasone. Timothy White. Stephen Davis. Jen Easterly. The quartet who drafted plans for US Cyber Command discussed their shared history in cyber defense.

Never Miss a Beat: Get a snapshot of the issues affecting the IT industry straight to your inbox.

.jpg?width=300&auto=webp&quality=80&disable=upscale)